Read Sharp SD-SH111 (serv.man14) Service Manual online

SD-SH111

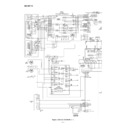

– 34 –

Figure 34 BLOCK DIAGRAM (1/17)

+B10

+B10

+B10

+B10

+B10

+B8

+B10

+B9

+B9

+B9

Q3302

Q3301

Q3303

FLGA

/DFTN

SCD

SCL

SCB

VRCK

FLGA

EXTAD

VRCK

SPV

FDD

SPDRV

SLDRV

DPDC

TEB

EOB

EOF

RFON

RFOP

RPZI

RFRP

LVL

TEI

FEI

156

159

158

TRD

TRD

FOD

SPDRV

SLDRV

41

/SVAL

O

SOSO_O

TR+

TR-

FO+

FO-

TR+

TR–

FO–

FO+

SW1

OPEN/CLOSE

SW4

PICKUP IN

M2

SLED

MOTOR

M1

SPINDLE

MOTOR

M

M

30

29

28

27

26

25

24

23

22

21

19

18

20

17

16

15

14

13

12

11

10

9

8

7

6

5

PD

LD

–

+

+

–

–

–

–

+

+

+

VE

VA

VB

VC

VF

Vref

Vcc

GND

HOLOGRAM

LASER UNIT

(CD)

GND

OSC

(DVD)

LASER UNIT

HOLOGRAM

GND

Vcc

Vref

VD

VC

VB

VA

PD

LD

+

+

+

–

–

–

–

+

4

3

2

1

ACTUATOR

IC3705

NJM2904M

OPE AMP.

–

–

+

+

6

5

7

3

2

1

1

5

6

7

IX

MICRO

TO DISPLAY

UNIT

CP3202

LD_FWD

LD_RVS

DVD_FUNC

CAM_SW

DISC1_SW

UART_RX

5

DVD_BUSY

6

DVD_DI

8

7

DVD_DO

9

DVD_CLK

3

4

D_GND

DVD_STB

C3207

56 UART_RXD

UART-RXD

EECS 62

FIP_CS

S/E_CK

S/E_DO

S/E_DI

KEY3 97 KEY3

2

7

4

5

6

3

IC3507

BR93L66F

EEPROM

55 SUB/EEP_DIN

53 SUB/EEP_DOUT

57 SUB/EEP_CLK

87

53 SUB/EEP_DOUT

57 SUB/EEP_CLK

87

5

4

2,3

IC3503

PST9125N

RESET

IC3508

IX1761GE

TRACK BUFFER I/F

IX1761GE

TRACK BUFFER I/F

VCC

AVCC

VSS

AVSS

70,69 LD_FWD/REV

61 IN_SW

68 LD_SW

100 EJ_SW

90 MUTE

67 CHOP

73 /RESET

71 G_RESET

72-65

5VBUS

N0O-N7O

77

79

91

78

80

92

93

94

HADR0-7 HDAT

PD

PSYCO

RAM

(4.2KByte)

MEMORY CTL

ERROR

DETECT

ID

DETECT

45,51,64

VDD2

VDD1

1,11,26,40,62,76,86

PDC

/

73

IC3

TC94

SERV

MD0-7

46-53

MD0-7

MICOM I/F

AVSS 149,154

PVSS 127

XVSS 9

DACVSS 3,8

VSS5 17,22,39,66

61,83,110

VSS3 105,122,171

V

X

5 DAC VDD

144,160 AVDD

138 PVDD

169 /DFCT

156

172 SCD

173 SCL

174 SCB

170 VRCK

37 FLGA

EXT_DA

TRO

FOO

DAC

DEMOD

SYNC D

PLL

SLICE

LEVEL

GEN.

163

162

166

164

167

168

DMO

FMO

DPDC

TEBC

EQBC

ANMON

DAC IF

(PWM)

139

143

142

146

153

152

151

150

DATA

SLICER

RFON

RFDVD

RFCD

DIGITAL SERVO

SERVO

CONTROL

DEQ

ADC

RFZI

RFRP

LVL

TEI

FEI

LVL

TEO

FEO

DPDB

TEB

EQB

EQF

RFON

RFOP

RPZ

RPO

LDP1

51

18,23,31,36

VDD

8

LDO2

4

4

MDI2

5

5

LDP2

57

57

15

14

13

22

42

47

2

DPD2

DPD1

DPBD

DPAC

12

11

10

9

IC3301

TA1323F

RF SIGNAL PROCESSOR

55

54

53

52

VRCK

VCKF

16

17

ADJUST

CONSTANT

TIME

45

APC2

DVD_LD

BUS

ADJUST

T-GAIN

ADJUST

F-GAIN

FE-GAIN

ADJUST

TE-GAIN

ADJUST

DETECT

CREATION

CREATION

LEVEL

3BTE

FE

ADJUST

R-GAIN

APCI

CD_LD

1,28

VCC

8

GND

19,29,30

10

LDP

LDP

LDN

9

OUTL

OUTR

LOADING DRIVER

MOTOR DRIVER

BA5984FP

IC3801

–

–

–

–

–

–

+

+

+

+

+

+

OPIN4(+)

OPIN3(+)

OPIN2(+)

25

22

7

26

23

6

27

24

5

16

18

11

OPOUT4

OPOUT3

OPOUT2

OPIN4(–)

OPIN3(–)

OPIN2(–)

TRP

FOP

SPP

–

–

–

SHIFT

–

15

17

12

LEVEL

–

–

–

+

+

+

+

+

+

TRN

FON

SPN

+

SHIFT

–

LEVEL

+

SHIFT

–

LEVEL

+

13

SLP

SLP

OPIN1(+)

2

3

4

20

OPIN1(–)

OPOUT1

BIAS

21

MUTE

–

+

SLN

14

–

+

SHIFT

LEVEL

+

–

+

–

–

+

DPDTE

CREATION

CREATION

EQ

CREATION

RF RIPPLE

46

Vcc

SHIFT

FWD,REV

1,39,56,62

19

20

21

35

33

43

44

29

30

25

26

SCD

SCL

SCB

DFTN

VrA

PITP

48 PITP

P2TP

3

P2TN

P1AI

P1BI

P1CI

P1DI

61

60

59

58

P2DI

P2CI

64

63

P2FN

P2FP

P2BI

P2AI

MDI1

LDOI

103

6,15,24,38,47,59,79,104

93

1,33,52,76,81

EECS

S/E_CS

+B10

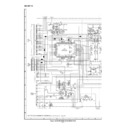

– 35 –

SD-SH111

Figure 35 BLOCK DIAGRAM (2/17)

+B10

+B10

+B10

+B10

+B10

0

+B9

N.C

41

42

43

47

48

49

52

53-60

/SOSO_I

/SVAL_I

SDCK_I

SDCK_O

/SVAL_O

SOSO_O

SD0_O-SD7_O

/SVAL_O

/SOSO_O

SDCK_O

/ERR_0

/WR,FRCS,/RD

CP3201

IC3662

1.8V RGE

IC3661

3.3V RGE

+B10

+B7

CP5001

CNV01

R3555

R3552

N.C

RY/BY 15

BYTE 47

WP 14

FL_RESET

A1-19

12 RP

D0-15

WE,/CE,/OE

/WR,FRCS,/RD

VSS 27,46

11,26,28

29-36,38-45

DO1-16

16-25,1-8,48

A0-18

IC3501

IX1689GE

FLASH ROM

VCC,VPP 37,13

VCC 1,6,20

OE 27

VSS 21,35,40

IC3502

IX0448AW

4M DRAM

A0-8

16-19,22-26

DQ1-16

2-4,7,8,31-34,36-39

16-19,22-26

DQ1-16

2-4,7,8,31-34,36-39

13,14

WE,RAS

29,28

LCAS,UCAS

LCAS,CAS

/WA,RAS

D0-15

A1-9

LCAS,CAS

/WA,RAS

D0-15

A1-9

LCAS,CAS 86,116

/HWR,RAS 84,118

D0-15 34-37,39-46,48-51

A0-19 2-5,7-14,16-23

VSS

A_5V

D_5V

M_GND

A_GND

D_GND

M_8V

V_8V

A_5V

D_5V

M_GND

A_GND

D_GND

M_8V

4,10,26

41,47,50

1,7,13,25,38,44

34 CKE

IC3602/3603

IX0449AW

16M SDRAM

15-17 WE,CAS,RAS

18 CS

35 CLK

35 CLK

14,36 LDOM/LDOU

21-24,27-32,20,19

A0-11

40,42,43,45,46,48,49

2,3,5,6,8,9,11,12,39

DQ0-15

RAMA0-11

RAMD0-15

RAMDOM

PCLK

RAMCS0(FOR IC3602)

RAMCS1(FOR IC3603)

RAMRAS

RAMWE,RAMCAS

21,35,40

1,6,20

IC3702

IX0447AW

4M EDO DRAM

2-5,7-10,31-34,36-39

16-19,22-26

28,29

14

27,13

16-19,22-26

28,29

14

27,13

DDAT0-15

DADR0-8

UCAS/LCAS

RAS

OE/WE

DADR0-8

UCAS/LCAS

RAS

OE/WE

N.C

R3613

27.0MHz

X3601

R3612

VCLKX2

127

XO

119

GCLK

120

117

115

118

I/F

PLL/CLOCK

GCLK

PLLCFG-I

PLLCFG-O

R3604

R3603

N.C

N.C

102

105

106

103

108

108

111

100

I/F

ENCODER

VIDEO

ANALOG

CVBS/G/Y

Y/R/V

C/B/U

IC3601

IX1720GE

DVD DECODER

CVBS

L.P.F

Q5001,5004

Q5007,5010

Q5002,5005

Q5008,5011

Y

L.P.F

Q5003,5006

Q5009,5012

C

L.P.F

Q3205

BUFF.

Q3203

BUFF.

BUFF.

Q3202

BUFF.

BUFF.

CVBS/C

RSET

VREF

CQSYNC

112

125

129

TEST-SIO

TESTMODE

I/F

ICEMODE

SCNENBL

N.C

N.C

N.C

N.C

92

96

93

95

FI

VSYNC

HSYNC

VCLK

VIDEO I/F

DIGITAL

62-60

57,59

68

64

50,47,45

42,41,43

46,48,51

54,53,55

91,88,85,82,79

76,74,70,88,72

75,78,81,84,87

90

SDRAM

I/F

RAMME

RAMCAS

RAMRAS

RAMCS0,1

PCLK

RAMDOM

RAMDAT0-15

RAMADD0-11

151

147

150

148

149

152-159

DVD-DSP

I/F

DVDREQ

DVDERR

DVDSTRB

DVDSOS

DVDVALID

DVDDAT0-7

D0-15

A1-4

/RD,/WR

AVCS

WAIT

N.C

AVINT

25-20

18,17

15,13

11,9-5

30-27

31,34

32

39

2

1

4

36

37

I/F

HOST

HD0-15

HA0-3

HWR,HRD

HCS

HACK

HWID

HORD

HTYPE

HRDY

HIRQ

N.C

N.C 143

134

PURPOSE

GPIS

GPSO

GPIO

GENERAL

145

N.C.

Z_RESET

Z_STNBY

124

122

160

RESET/

STANDBY/

I/F

STATUS

STNBY

RESET

IDLE

L3602

L3601

3,16,26,38,44,52,58,67

71,77,83,89,94,98,126

135,140,19,99

130

104

FB3605

121

12,33,63,116,142

N.C

N.C

N.C

N.C

N.C

I/F

AUDIO

DIGITAL

AIN

AOUT0-3

AMCLK

ALRCLK

ABCLK

S/PDIF

113

136-138

136-138

131

139

141

133

FB3604

101,107,109,110

123,132

10,40,49,56,65,69

80,86,97,128,145,146

14,35,73,114,144

IC3504

IX1687GE

MICROCOMPUTER

/HWR,FROM_CS,/RD 84,120,83

F

FL3501

(20MHz)

77

78

XTAL

EXTAL

HGA_CS

ADAC_DA

ADAC_CK

ADAC_L

AMUTE2

UART_RXD

UART_CTL

S1_H

VMUTE

/SRV_INT

WAIT

SRV_CS

/MA

Z_RESET

Z_STNBY

AV-INT

HGA_INT

AV-CS

60

110

111

112

88

56

58

108

109

31

92

117

66

65

64

30

26

119

38

30-37

VSS 10,25,29,39,44,50

61,63,75,85,100

PDON8O

PDON0O-N7O

OPD

I/F

72-65

5VBUS

N0O-N7O

IPD I/F

77

HOST I/F

HADR0-7 HDAT0-7 HRD HWR HAS HCS1 HCS2

PDI(0)-(7)

/ERR_1

TIMING GEN.

PDRQI

PDRQO

PSYCI

PDCKI

PDCKO

PSYCO

64

2

/RST 40

/MINT 45

/MA 41

42,43

/MDR,/MWR

/MCE 44

XO

XI

11

10

FL3701

(22.5792MHz)

PDCK

/PDRQ

/PSYC

73 72 71

IC3701

TC94A03F

SERVO ECC

SD0_1,SD7_1

60,62-65,67-69

70

PD0-7

PDB

MD0-7

46-53

OUTPUT I/F

MD0-7

MICOM I/F

ECC

90,94

91

92,93

79-82,84-88

DRAM

I/F

106-109,111-113

96-104

VDD5 54,74,95

VDD3 16,33,59

78,89,116

XVDD 12

5 DAC VDD

144,160 AVDD

DEMODULATION

SYNC DET.

PLL

SLICE

EVEL

GEN.

RVO

O

ROL

+B10

+B10

+B10

+B10

+B10

+B10

D_1.8V

D_3.3V

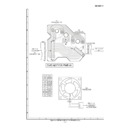

SD-SH111

– 36 –

4

3

1

3

1

5 6 7 8

4 3 2 1

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

2

2

RECOUT2A

A_+12V

A_+7V

A_–7V

C_IN

R_OUT

R_IN

SR_IN

SW_IN

L_IN

L_OUT

SL_IN

IND1

IND1

IND2

D_+3.3V

BASS_SW

TU_MUTE

CNP306

TO DSP PWB

TUNER_SM

SD_ST_IN

CCB_DO

CCB_CL

CCB_DI

CCB_CE

+11.5V_RELAY

D_+5V

+3.7V_STAND-BY

MON_OUT1A

MON_OUT2A

MON_OUT2

MON_OUT1

W_SP_RLY

INE1

INE2

RECOUT1A

PROTECT

VOL_STB

VOL_DATA

VOL_CLK

OFFSET

V_SEL1

SPDIF

V_SEL4

L_MUTE

V_SEL3

V_SEL2

INB2

INA1

INB1

INA2

INB2

INA2

INB1

IND2

VOL_DATA

VOL_CLK

VOL_STB

F_SP_RLY

FAN_MOTOR

S_SP_RLY

C_SP_RLY

W_SP_RLY

-B_CONT

S_MUTE

H.P_SW

D_GND

INA1

INF1

INF2

LATCH

DATA

CLOCK

DVDD

AVSS

SWCHAIN

SWCHBIN

SWCHOUT

CCHOUT

CCHBIN

CCHAIN

DGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

AGND

SLCHOUT

SRCHOUT

RCHBBI

LCHBBI

LCHBBO

RCHBBO

RCHOUT

LCHOUT

LCHAIN

LCHBIN

SLCHBIN

SLCHAIN

SRCHAIN

SRCHBIN

RCHBIN

RCHAIN

SWOUT

TONEOUT2

TONEOUT1

TCA1

TCB1

TCC1

TCC2

TCB2

TCA2

TINA2

TINB2

TINB1

TINA1

SELOUT1

SELOUT2

RECOUT2A

RECOUT2B

RECOUT1B

RECOUT1A

ING2

ING1

INF1

INF2

INE2

INE1

IND1

IND2

INC2

INC1

INB1

INB2

INA2

INA1

AVDD

AVDD

NC

NC

NC

NC

NC

NC

NC

NC

NC

6

5

7

4

8

3

9

10

2

1

8

9

9

7

6

5

4

3

2

1

32

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

10

11

12

13

14

15

8

9

9

7

6

5

4

3

2

1

10

11

12

13

14

15

8

9

9

7

6

5

4

3

2

1

10

11

12

13

14

15

9

8

7

6

5

4

3

2

1

1

TO DSP PWB

CNP101

FROM

DISPLAY PWB

TO

MAIN PWB (2/2)

TO MAIN PWB

TO MAIN PWB

TO MAIN PWB

CNSE02

–

–

+

+

VSS

VDD

10 11 12 13

40

9

1

2

3

4

5

6

7

8

18

15

BASS_SW

CNS306

CNS101

CNW101

CNP502

IC510

NJM4580M

OPE AMP.

IC501

M61501FP

6CH VOLUME

Q525

Q526

Q527

IC509

NJM7805D

VOLTAGE REGULATOR

IC508

IX0445AW

VOLTAGE

REGULATOR

Q531

Q532

Q533

Q5

Q501

Q502

IC

NJM

OPE

OPE

IC

NJM4

OPE

OPE

Q506

I

NJM

OP

OP

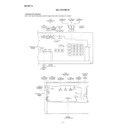

Figure 36 BLOCK DIAGRAM (3/17)

– 37 –

SD-SH111

CNSA106A

FROM

HEADPHONES PWB

CNS04

TO SPEAKER PWB

CNS503

CNSA106B

CNSA106C

M

8

4

5 6 7 8

4 3 2 1

5 6 7 8

4 3 2 1

5 6 7 8

4 3 2 1

5 6 7 8

4 3 2 1

5

6

7

3

2

1

FAN_MOTOR

PROTECT

FAN_L/H

RIMIT

A_–12V

H.P_R

H.P_L

H.P_SW

OFFSET

S_MUTE

PROTECT

S_SP_RLY

FAN_L/H

W_SP_RLY

–B_CONT

F_SP_RLY

C_SP_RLY

+11.5V_RELAY

A_+12V

1

2

3

1

2

3

2

3

4

3

2

2

5

1

9

10

11

12

13

14

15

8

7

6

5

4

3

2

1

1

15

SURROUND R-CH

SURROUND L-CH

CENTER

SUB WOOFER

FRONT L-CH

FRONT R-CH

7

8

9

1

3

2

2

4

5

6

7

8

9

1

3

2

2

4

5

6

2

3

1

2

3

1

2

3

1

2

1

–

+

VSS

+

–

VDD

VDD

–

–

+

+

VSS

VDD

–

–

+

+

VSS

VDD

VSS

+

+

–

–

VSS

+

+

–

–

VDD

+B

TO 1BIT AMP. PWB

TO 1BIT AMP. PWB

TO 1BIT AMP. PWB

FROM

SUBWOOFER

OUT PWB

CNS506

SD_ST_IN

TU_MUTE

CCB_CL

CCB_DI

CCB_CE

CCB_DO

TUNER_SM

INE1

INE2

2

7

5

1

1

4

3

6

9

10

11

12

13

14

15

15

8

R OUT

TUNED

MUTE

STEREO

CL

GND

VDD +3.3V

DI

VCC +12V

COMP

L OUT

GND

FM VSM

DO

CE

TO

TUNER UNIT

TUN1

CNP507

CNW507

RT16

10K

Q504

Q505

Q503

IC502

NJM4580M

OPE AMP.

OPE AMP.

IC503

NJM4580M

OPE AMP.

OPE AMP.

Q506

IC504

NJM4580M

OPE AMP.

OPE AMP.

Q515

Q514

Q510

Q509

Q513

Q508

Q507

IC505

NJM4565D

MIC AMP.

Q517

Q516

Q518

Q512

Q529

Q520

Q522

Q521

Q523

Q524

CNP505

CNS505

CNP504

CNP503

CNW503

CNP508 CNW508A CNW508B

M4

FAN MOTOR

CNW508C

CNW508D

CNP506

Q530

IC506

NJM4580M

OPE AMP.

OPE AMP.

Q511

Figure 37 BLOCK DIAGRAM (4/17)